# MIPS64<sup>TM</sup> 20Kc<sup>TM</sup> Processor Core User's Manual

Document Number: MD00126 Revision 01.10 Sept 28, 2002

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2002 MIPS Technologies Inc. All rights reserved.

Copyright © 2002 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) are reserved under the Copyright Laws of the United States of America.

If this document is provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format), then its use and distribution is subject to a written agreement with MIPS Technologies, Inc. ("MIPS Technologies"). UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY WITHOUT THE EXPRESS WRITTEN CONSENT OF MIPS TECHNOLOGIES.

This document contains information that is proprietary to MIPS Technologies. Any copying, reproducing, modifying, or use of this information (in whole or in part) which is not expressly permitted in writing by MIPS Technologies or a contractually-authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

MIPS Technologies or any contractually-authorized third party reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error of omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Any license under patent rights or any other intellectual property rights owned by MIPS Technologies or third parties shall be conveyed by MIPS Technologies or any contractually-authorized third party in a separate license agreement between the parties.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or any contractually-authorized third party.

MIPS<sup>®</sup>, R3000<sup>®</sup>, R4000<sup>®</sup>, R5000<sup>®</sup> and R10000<sup>®</sup> are among the registered trademarks of MIPS Technologies, Inc. in the United States and certain other countries, and MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>, MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, MIPS-3D<sup>TM</sup>, MIPS-based<sup>TM</sup>, MIPS II<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS IV<sup>TM</sup>, MIPS V<sup>TM</sup>, MDMX<sup>TM</sup>, MIPSsim<sup>TM</sup>, MIPSsimCA<sup>TM</sup>, MIPSsimIA<sup>TM</sup>, QuickMIPS<sup>TM</sup>, SmartMIPS<sup>TM</sup>, MIPS Technologies logo, 4K<sup>TM</sup>, 4Kc<sup>TM</sup>, 4Km<sup>TM</sup>, 4Ke<sup>TM</sup>, 4KEc<sup>TM</sup>, 4KEc<sup>TM</sup>, 4KEm<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KS<sup>TM</sup>, 4KS<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kf<sup>TM</sup>, 20K<sup>TM</sup>, 20Kc<sup>TM</sup>, 25Kf<sup>TM</sup>, R4300<sup>TM</sup>, ASMACRO<sup>TM</sup>, ATLAS<sup>TM</sup>, BusBridge<sup>TM</sup>, CoreFPGA<sup>TM</sup>, CoreLV<sup>TM</sup>, EC<sup>TM</sup>, JALGO<sup>TM</sup>, MALTA<sup>TM</sup>, MGB<sup>TM</sup>, PDtrace<sup>TM</sup>, SEAD-2<sup>TM</sup>, SOC-it<sup>TM</sup>, The Pipeline<sup>TM</sup>, and YAMON<sup>TM</sup> are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

Template: B1.06, Build with Conditional Tags: 2B 20KC

Copyright © 2002 MIPS Technologies Inc. All rights reserved.

### Table of Contents

| Chapter 1 Introduction to the 20Kc Processor                                                     | 1  |

|--------------------------------------------------------------------------------------------------|----|

| 1.1 Features                                                                                     |    |

| 1.2 Architectural Overview                                                                       |    |

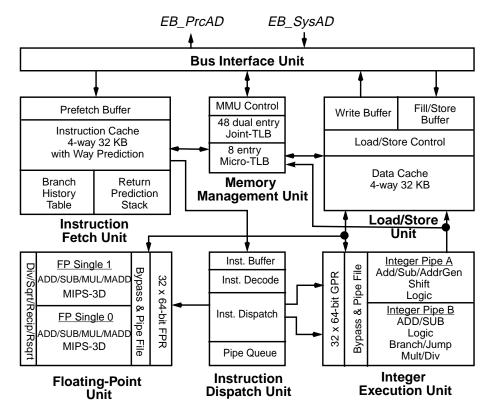

| 1.2.1 Instruction Fetch Unit                                                                     | 4  |

| 1.2.2 Instruction Dispatch Unit                                                                  | 4  |

| 1.2.3 Integer Execution Unit                                                                     |    |

| 1.2.4 Floating-Point Unit                                                                        |    |

| 1.2.5 Load/Store Unit                                                                            |    |

| 1.2.6 Memory Management Unit                                                                     |    |

| 1.2.7 Bus Interface Unit                                                                         |    |

| 1.2.8 EJTAG Unit                                                                                 |    |

| 1.3 System Overview                                                                              |    |

| Chapter 2 Instruction Set Overview                                                               | 7  |

| 2.1 CPU Instruction Formats                                                                      | 7  |

| 2.2 Load and Store Instructions                                                                  |    |

| 2.2.1 Scheduling for Load Use Latencies                                                          |    |

| 2.2.2 Defining Access Types                                                                      |    |

| 2.3 Computational Instructions                                                                   |    |

| 2.3.1 Multiply and Divide Instructions                                                           |    |

| 2.4 Jump and Branch Instructions                                                                 |    |

| 2.4.1 Overview of Jump Instructions                                                              |    |

| 2.4.2 Overview of Branch Instructions                                                            |    |

| 2.5 Control Instructions                                                                         |    |

| 2.6 Coprocessor Instructions                                                                     |    |

| 2.7 Enhancements to the MIPS Architecture                                                        |    |

| Chapter 3 Pipeline                                                                               | 13 |

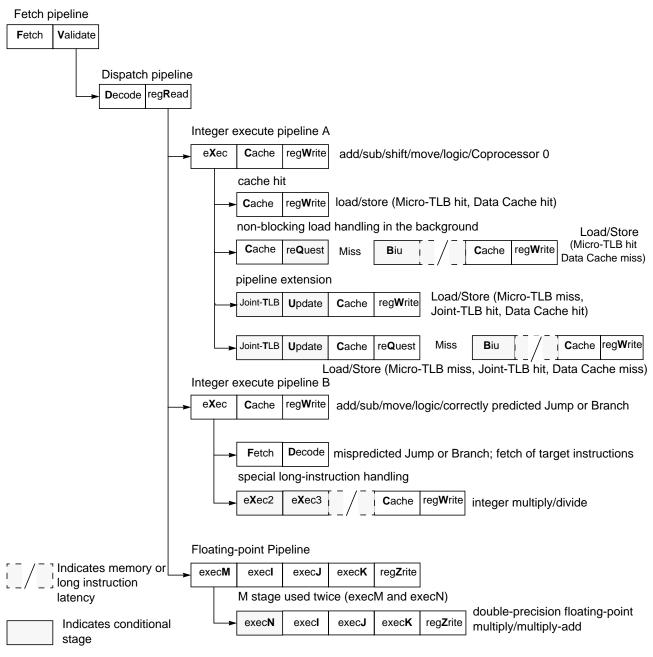

| 3.1 Pipeline Overview                                                                            |    |

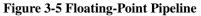

| 3.2 Fetch Pipeline                                                                               |    |

| 3.2.1 F Stage: Instruction Fetch                                                                 |    |

| 3.2.2 V Stage: Validate                                                                          |    |

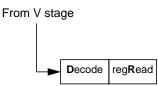

| 3.3 Dispatch Pipeline                                                                            |    |

| 3.3.1 D Stage: Instruction Decode                                                                |    |

| 3.3.2 R Stage: Register File Read                                                                |    |

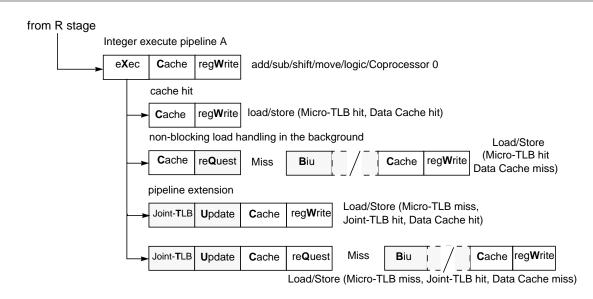

| 3.4 Integer and Load/Store Pipelines                                                             |    |

| 3.4.1 Integer Pipeline A                                                                         |    |

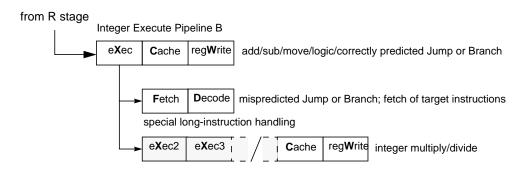

| 3.4.2 Integer Pipeline B                                                                         |    |

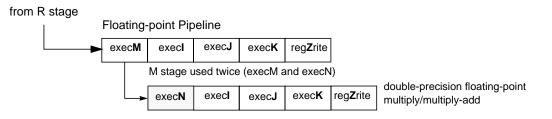

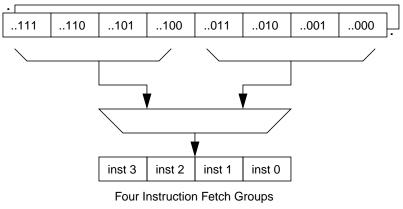

| 3.5 Floating-Point Pipeline                                                                      |    |

| 3.5.1 M Stage: FP Multiplier Array - First Pass                                                  |    |

| 3.5.2 N Stage: FP Multiplier Array - Second Pass                                                 |    |

| 3.5.3 I Stage: FP Multiply Completion                                                            |    |

| 3.5.4 J Stage: FP Add                                                                            |    |

| 3.5.5 K Stage: FP Normalization                                                                  |    |

| 3.5.6 Z Stage: FPR Write                                                                         |    |

| 3.6 Instruction Latencies and Repeat Rates                                                       |    |

| 3.7 Instruction Eatencies and Repeat Rates                                                       |    |

|                                                                                                  |    |

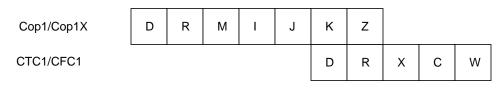

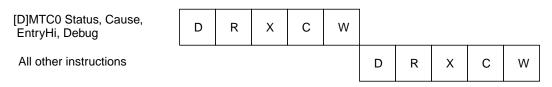

| <ul><li>3.8 Instruction Dispatch Rules</li><li>3.9 Dispatch of Privileged Instructions</li></ul> |    |

| Chapter 4 Memory Management                                                                      |    |

| Chapter + Memory Management                                                                      |    |

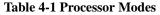

| 4.1 Operating Modes                                                                       |    |

|-------------------------------------------------------------------------------------------|----|

| 4.2 Other Modes                                                                           |    |

| 4.2.1 64-bit Address Enable                                                               |    |

| 4.2.2 64-bit Operations Enable                                                            |    |

| 4.2.3 64-bit FPR Enable                                                                   |    |

| 4.3 Processor Mode Selection                                                              | 35 |

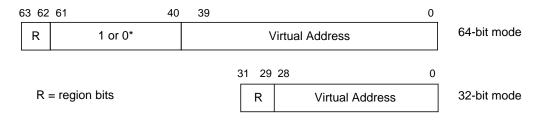

| 4.4 Addressing Modes                                                                      | 35 |

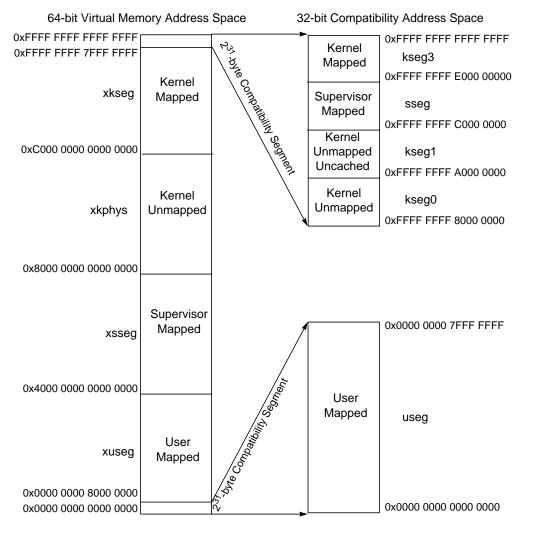

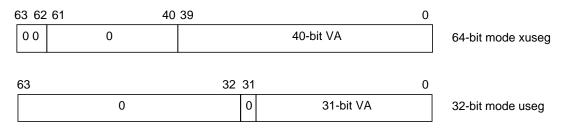

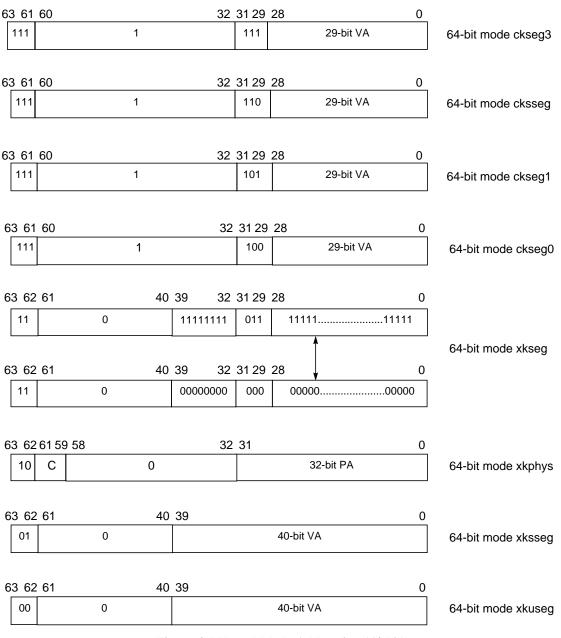

| 4.5 Address Space                                                                         |    |

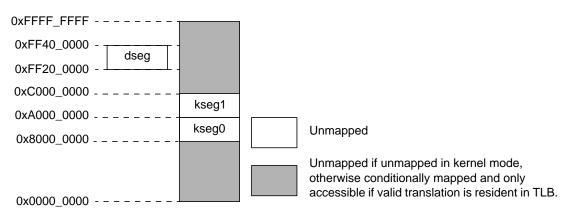

| 4.5.1 Access Control as a Function of Address and Operating Mode                          |    |

| 4.5.2 Address Translation and Cache Coherency Attributes for the kseg0 and kseg1 Segments | 40 |

| 4.5.3 Address Translation and Cache Coherency Attributes for the xkphys Segment           | 41 |

| 4.5.4 Address Translation for the kuseg Segment when Status <sub>ERL</sub> = 1            | 42 |

| 4.5.5 Special Behavior for the kseg3 Segment when Debug <sub>DM</sub> = 1                 | 42 |

| 4.5.6 Special Behavior for Data References in User Mode with $Status_{UX} = 0$            | 43 |

| 4.6 Address Segments                                                                      | 43 |

| 4.6.1 User Mode Segments                                                                  | 43 |

| 4.6.2 Supervisor Mode Segments                                                            | 44 |

| 4.6.3 Kernel Mode Segments                                                                | 46 |

| 4.6.4 Debug Mode                                                                          |    |

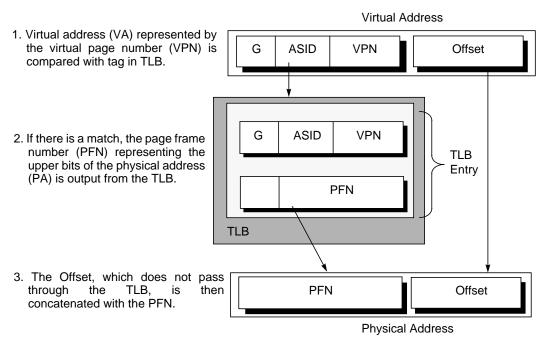

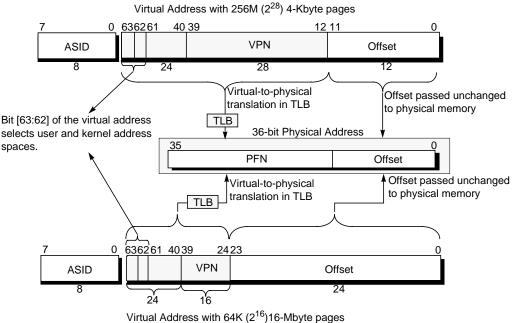

| 4.7 Virtual Address Translation                                                           |    |

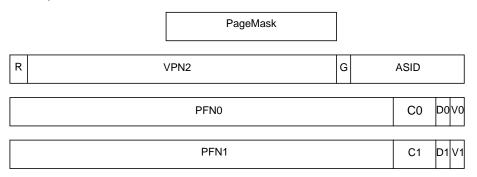

| 4.7.1 Page Size Support                                                                   |    |

| 4.7.2 Address Space Identifiers and Global Processes                                      |    |

| 4.7.3 Address Translation Mechanism                                                       |    |

| 4.8 Translation Lookaside Buffers                                                         |    |

| 4.8.1 20Kc TLB Organization                                                               |    |

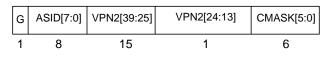

| 4.8.2 TLB Tag and Data Formats                                                            |    |

| 4.9 TLB Instructions                                                                      |    |

| 4.9.1 Hits, Misses, and Multiple Matches                                                  |    |

| 4.9.2 Page Sizes and Replacement Algorithm                                                |    |

|                                                                                           | 50 |

| Chapter 5 Exceptions and Interrupts                                                       |    |

| 5.1 Exception Conditions                                                                  |    |

| 5.2 Exception Types                                                                       |    |

| 5.3 Exception Priority                                                                    |    |

| 5.4 Exception Vector Locations                                                            |    |

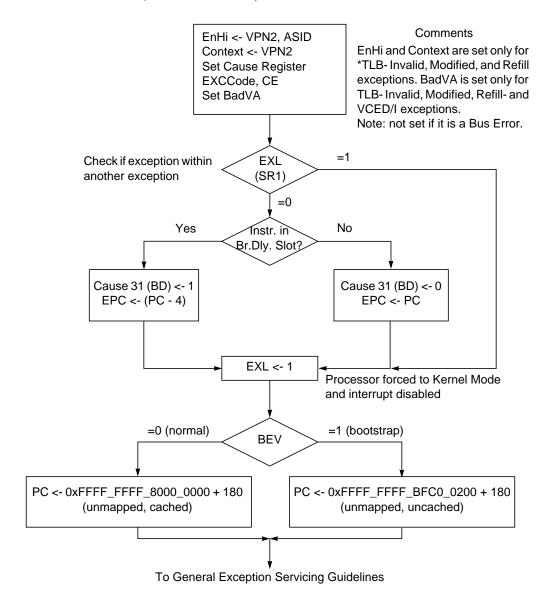

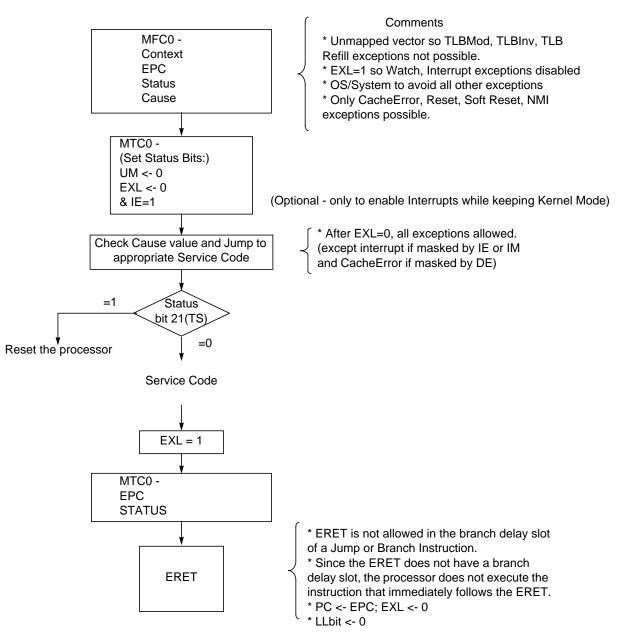

| 5.5 General Exception Processing                                                          |    |

| 5.6 Debug Exception Processing                                                            |    |

| 5.7 Exceptions                                                                            |    |

| 5.7.1 Reset Exception                                                                     |    |

| 5.7.2 Soft Reset Exception                                                                |    |

| 5.7.3 Debug Single Step Exception                                                         |    |

| 5.7.4 Debug Interrupt Exception                                                           |    |

| 5.7.5 Debug Instruction Break Exception                                                   |    |

| 5.7.6 Non-Maskable Interrupt (NMI) Exception                                              |    |

| 5.7.7 Machine Check Exception                                                             | 67 |

| 5.7.8 Bus Error Exception — Instruction Fetch or Data Access                              |    |

| 5.7.9 Cache Error Exception                                                               | 68 |

| 5.7.10 Interrupt Exception                                                                | 69 |

| 5.7.11 Debug Software Breakpoint Exception                                                | 69 |

| 5.7.12 Watch Exception — Instruction Fetch or Data Access                                 |    |

| 5.7.13 Address Error Exception — Instruction Fetch/Data Access                            |    |

| 5.7.14 TLB Refill and XTLB Refill Exceptions                                              |    |

| 5.7.15 TLB Invalid Exception — Instruction Fetch or Data Access                           |    |

| 5.7.16 Execution Exception — System Call                                                  | 72 |

| 5.7.17 Execution Exception — Breakpoint                                                   | 72 |

| 5.7.18 Execution Exception — Reserved Instruction                                         | 73 |

|                                                                                           |    |

| 5.7.19 Execution Exception — Coprocessor Unusable                    | 74  |

|----------------------------------------------------------------------|-----|

| 5.7.20 Execution Exception — Integer Overflow                        |     |

| 5.7.21 Execution Exception — Trap                                    |     |

| 5.7.22 Precise Debug Data Break Exception                            |     |

| 5.7.23 Imprecise Debug Data Break Exception                          |     |

| 5.7.24 TLB Modified Exception — Data Access                          |     |

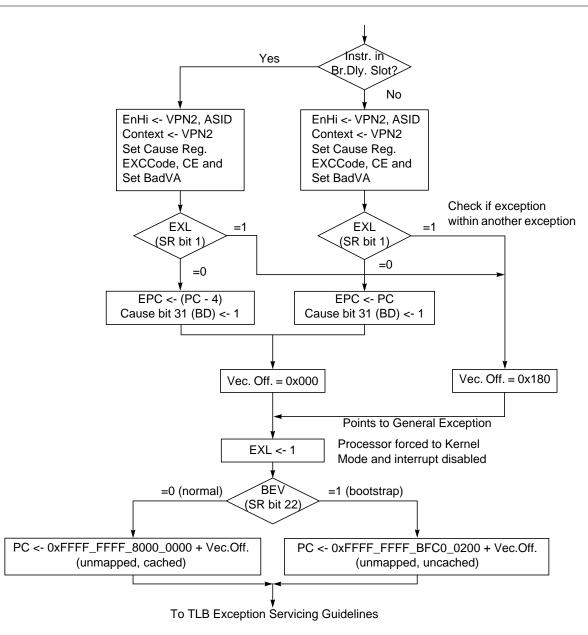

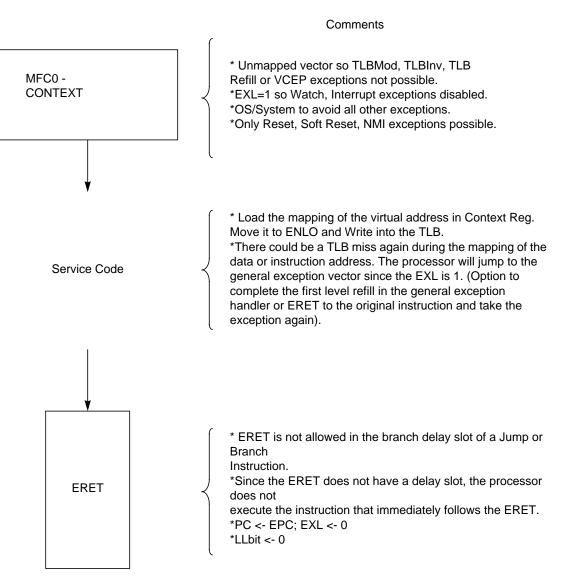

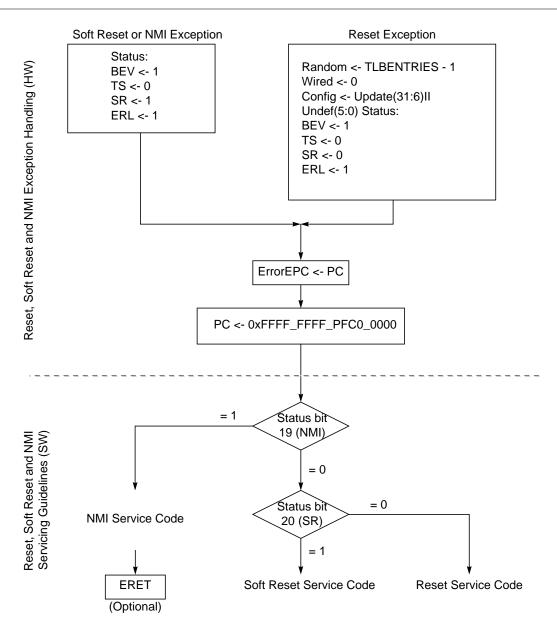

| 5.8 Exception Handling and Servicing Flowcharts                      |     |

| 5.9 Interrupts                                                       |     |

|                                                                      |     |

| Chapter 6 Coprocessor Registers                                      |     |

| 6.1 CP0 Register Summary                                             |     |

| 6.2 CP0 Registers                                                    |     |

| 6.2.1 Index Register (CP0 Register 0, Select 0)                      |     |

| 6.2.2 Random Register (CP0 Register 1, Select 0)                     |     |

| 6.2.3 EntryLo0, EntryLo1 (CP0 Registers 2 and 3, Select 0)           |     |

| 6.2.4 Context Register (CP0 Register 4, Select 0)                    |     |

| 6.2.5 PageMask Register (CP0 Register 5, Select 0)                   |     |

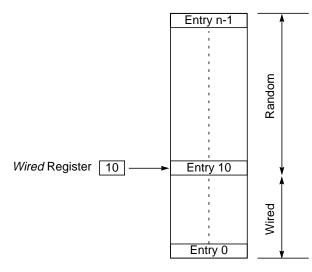

| 6.2.6 Wired Register (CP0 Register 6, Select 0)                      |     |

| 6.2.7 BadVAddr Register (CP0 Register 8, Select 0)                   |     |

| 6.2.8 Count Register (CP0 Register 9, Select 0)                      |     |

| 6.2.9 EntryHi Register (CP0 Register 10, Select 0)                   |     |

| 6.2.10 Compare Register (CP0 Register 11, Select 0)                  |     |

| 6.2.11 Status Register (CP0 Register 12, Select 0)                   |     |

| 6.2.12 Cause Register (CP0 Register 13, Select 0)                    |     |

| 6.2.13 Exception Program Counter (CP0 Register 14, Select 0)         |     |

| 6.2.14 Processor Identification (CP0 Register 15, Select 0)          |     |

| 6.2.15 Config Register (CP0 Register 16, Select 0)                   |     |

| 6.2.16 Config1 Register (CP0 Register 16, Select 1)                  |     |

| 6.2.17 Load Linked Address (CP0 Register 17, Select 0)               |     |

| 6.2.18 WatchLo Register (CP0 Register 18)                            |     |

| 6.2.19 WatchHi Register (CP0 Register 19)                            |     |

| 6.2.20 XContext Register (CP0 Register 20)                           |     |

| 6.2.21 Debug Register (CP0 Register 23)                              |     |

| 6.2.22 Debug Exception Program Counter Register (CP0 Register 24)    |     |

| 6.2.23 Performance Counter Registers (CP0 Register 25, Selects 0, 1) |     |

| 6.2.24 DErrCtl Register (CP0 Register 26, Select 0)                  |     |

| 6.2.25 IErrCtl Register (CP0 Register 26, Select 1)                  |     |

| 6.2.26 CacheErr Register (CP0 Register 27, Select 0)                 |     |

| 6.2.27 ITagLo Register (CPO Register 28, Select 0)                   |     |

| 6.2.28 IDataLo Register (CP0 Register 28, Select 1)                  |     |

| 6.2.29 DTagLo Register (CP0 Register 28, Select 2)                   |     |

| 6.2.30 DDataLo Register (CP0 Register 28, Select 3)                  |     |

| 6.2.31 ITagHi Register (CP0 Register 29, Select 0)                   |     |

| 6.2.32 IDataHi Register (CP0 Register 29, Select 1)                  |     |

| 6.2.33 DTagHi Register (CP0 Register 29, Select 2)                   |     |

| 6.2.34 DDataHi Register (CP0 Register 29, Select 3)                  |     |

| 6.2.35 ErrorEPC (CP0 Register 30, Select 0)                          |     |

| 6.2.36 DESAVE Register (CP0 Register 31)                             |     |

| 6.3 CP0 Hazards                                                      |     |

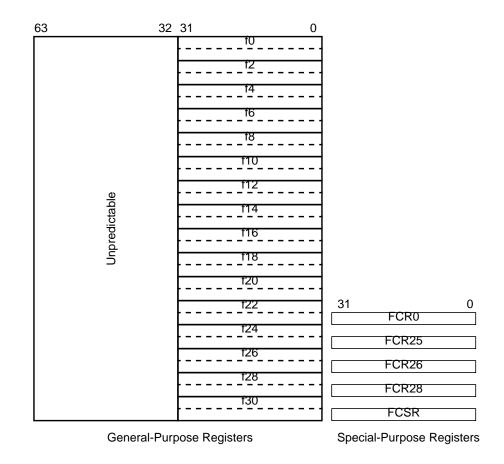

| 6.4 CP1 Register Summary                                             |     |

| 6.5 CP1 Registers                                                    |     |

| 6.5.1 Floating-Point Implementation Register (CP1 Register 0)        |     |

| 6.5.2 Floating-Point Condition Codes Register (CP1 Register 25)      |     |

| 6.5.3 Floating-Point Exceptions Register (CP1 Register 26)           |     |

| 6.5.4 Floating-Point Enables Register (CP1 Register 28)              |     |

| 6.5.5 Floating-Point Control and Status Register (CP1 Register 31)   | 126 |

| Chapter 7 Caches                                                        |     |

|-------------------------------------------------------------------------|-----|

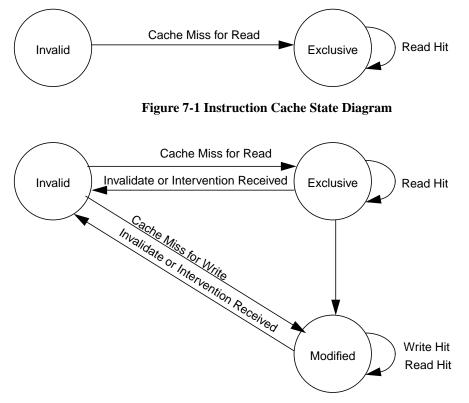

| 7.1 Instruction Cache                                                   |     |

| 7.1.1 Memory Management implications of the Virtual I-Cache             |     |

| 7.2 Data Cache                                                          |     |

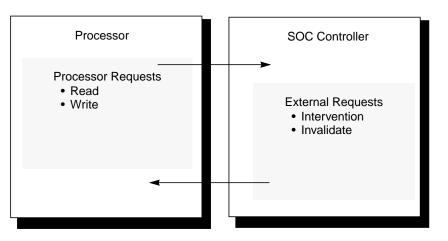

| 7.3 Cache Protocol                                                      |     |

| 7.4 Cache Attributes                                                    |     |

| 7.4.1 Uncached                                                          |     |

| 7.4.2 Uncached Accelerated                                              |     |

| 7.4.3 Non-Coherent Write-Back                                           |     |

| 7.4.4 Coherent Exclusive Write-Back                                     |     |

| 7.4.5 Non-Coherent, Write-Through with No Write-Allocate                |     |

| 7.4.6 Encoding                                                          |     |

| Chapter 8 Bus Interface Unit                                            | 135 |

| 8.1 20Kc System Interface Features                                      |     |

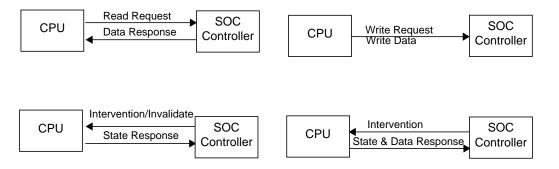

| 8.1.1 Processor and External Requests                                   |     |

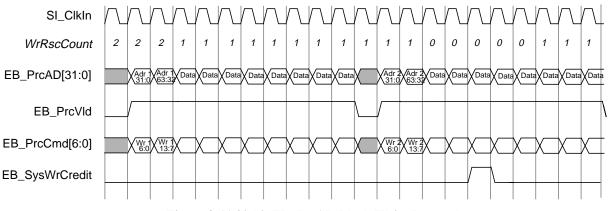

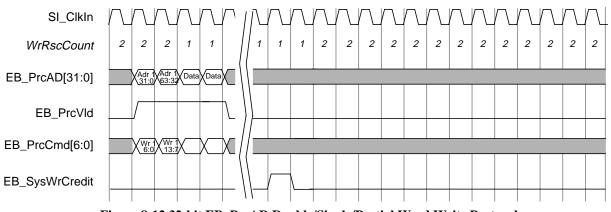

| 8.1.2 Multiplexed Unidirectional 32-bit Processor Address/Data Bus      |     |

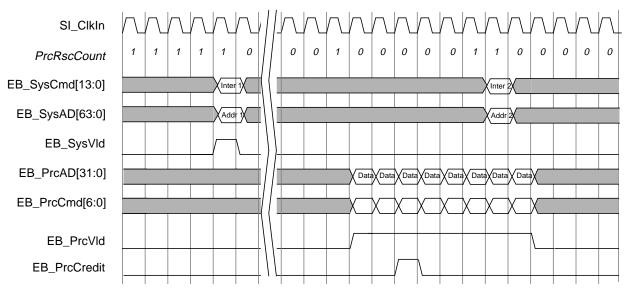

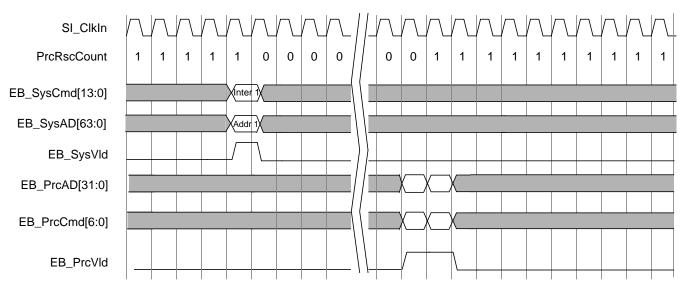

| 8.1.3 Multiplexed Unidirectional 64-bit SOC Controller Address/Data Bus |     |

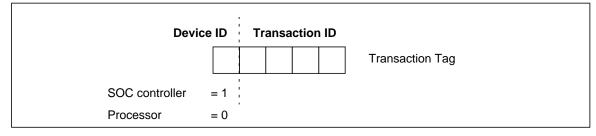

| 8.1.4 Support for Multiple Outstanding Split Transactions               |     |

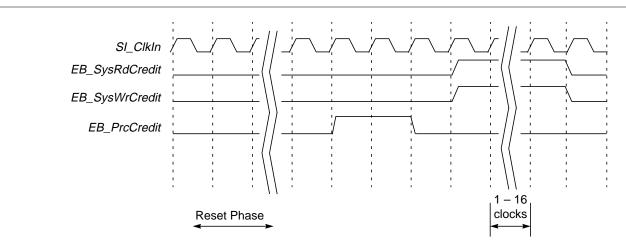

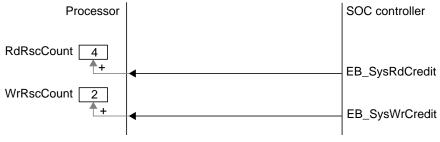

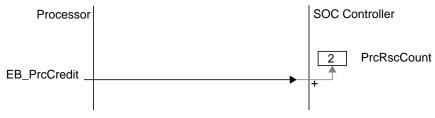

| 8.1.5 Credit-Based Flow Control                                         |     |

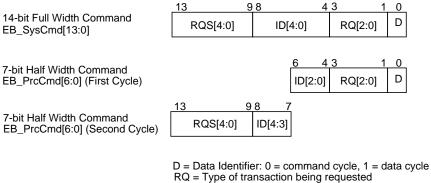

| 8.2 Bus Encoding (64-bit EB_SysAD Mode)                                 |     |

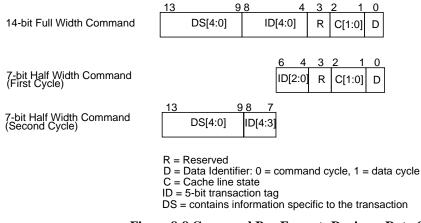

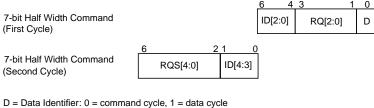

| 8.2.1 PrcCmd/SysCmd Bus Encoding (Command Cycles)                       |     |

| 8.2.2 PrcCmd/SysCmd Bus Encoding (Data Cycles)                          |     |

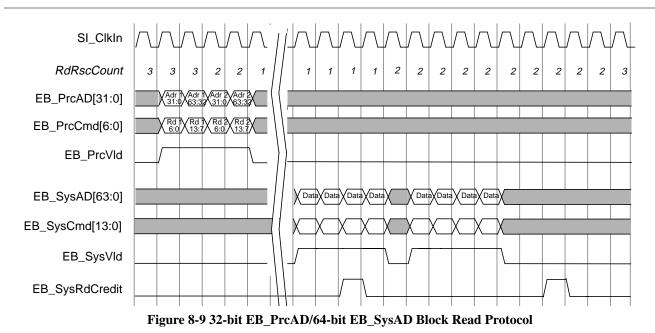

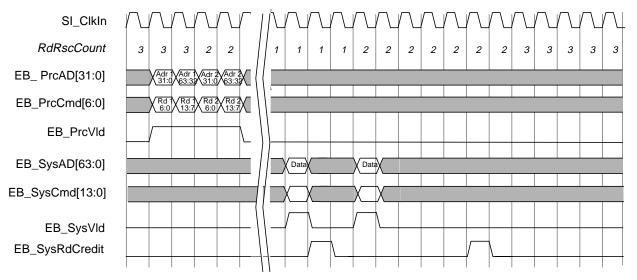

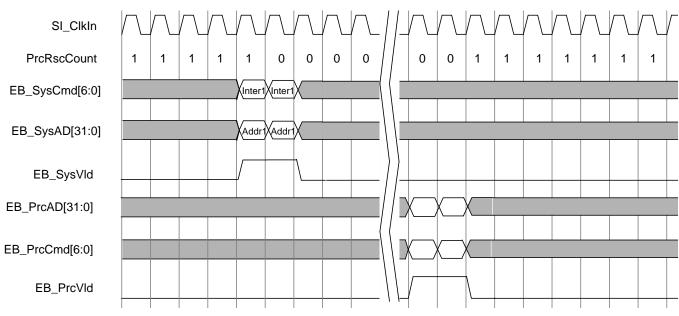

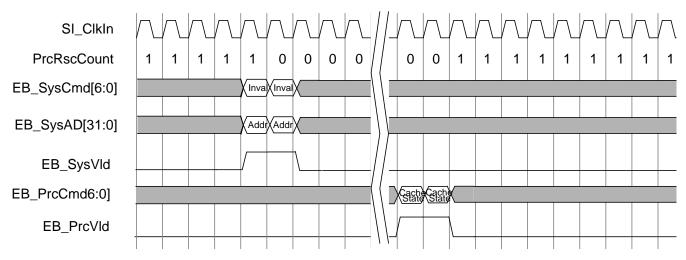

| 8.3 Processor and External Request Protocols (64-bit EB_SysAD Mode)     |     |

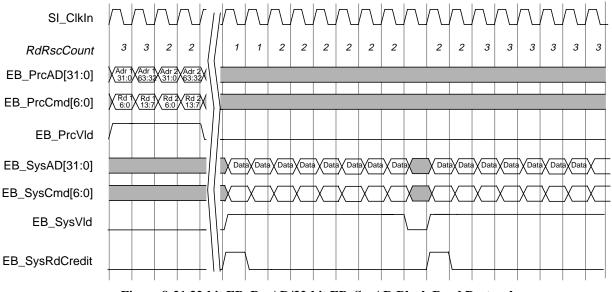

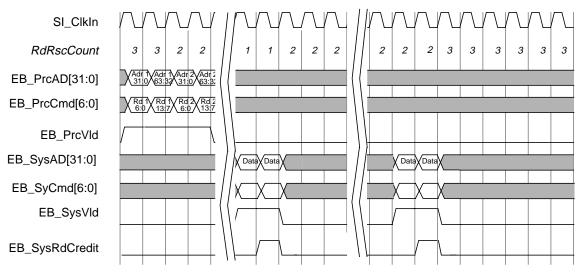

| 8.3.1 Processor Requests                                                |     |

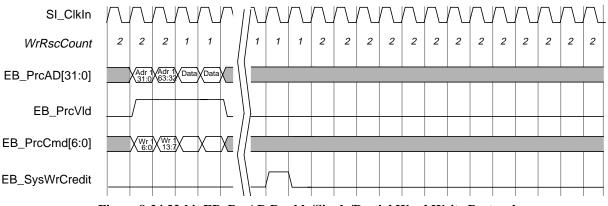

| 8.3.2 External Requests                                                 |     |

| 8.3.3 Coherency Conflicts                                               |     |

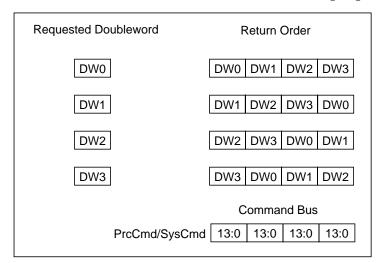

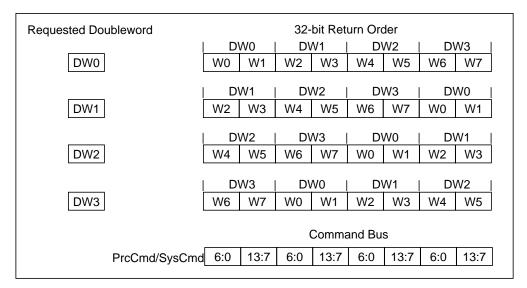

| 8.3.4 Data Ordering                                                     |     |

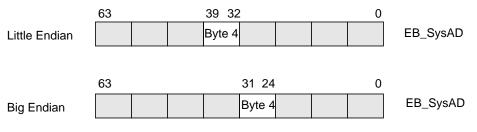

| 8.3.5 Data Alignment                                                    |     |

| 8.3.6 Dual Multiplexed Address and Data Buses                           |     |

| 8.4 Bus Encoding (32-bit EB_SysAD Mode)                                 |     |

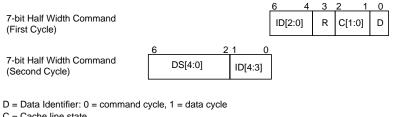

| 8.4.1 PrcCmd/SysCmd Bus Encoding (Command Cycles)                       |     |

| 8.5 Processor and External Request Protocols (32-bit EB_SysAD Mode)     |     |

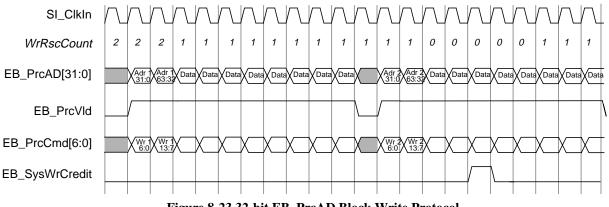

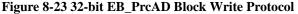

| 8.5.1 Processor Requests                                                |     |

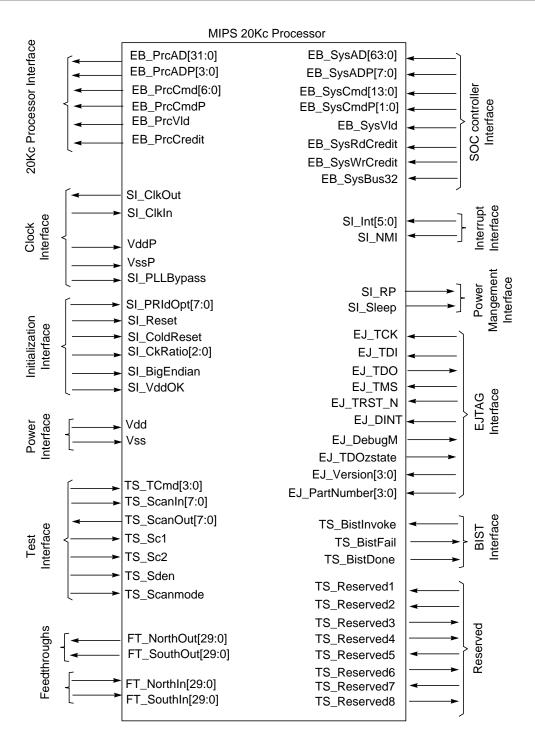

| 8.6 20Kc Signal Descriptions                                            |     |

|                                                                         |     |

| Chapter 9 Reset and Initialization                                      |     |

| 9.1 Processor Reset Signals                                             |     |

| 9.2 Processor Initialization Signals                                    |     |

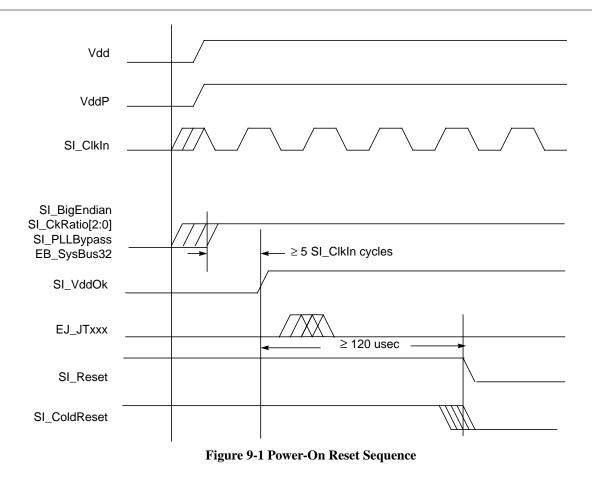

| 9.3 Reset Sequences                                                     |     |

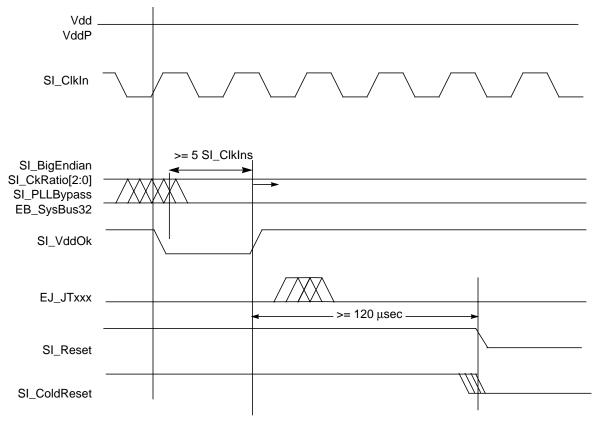

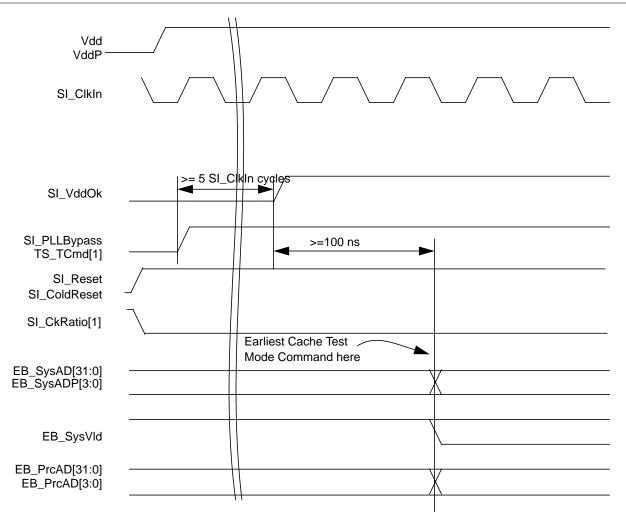

| 9.3.1 Power-On Reset Sequence                                           |     |

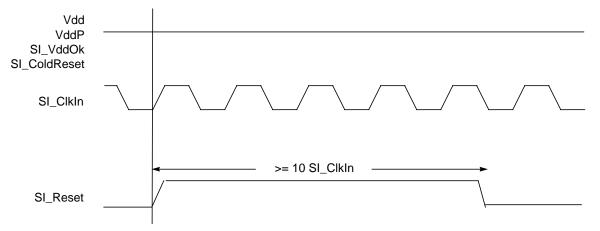

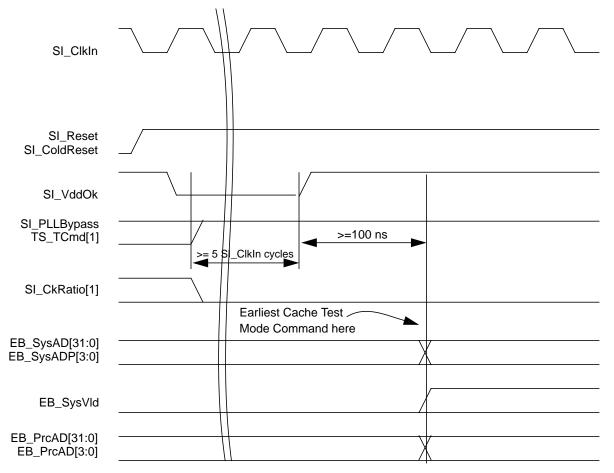

| 9.3.2 ColdReset Sequence                                                |     |

| 9.3.3 Warm Reset Sequence                                               |     |

| Chapter 10 Power Management                                             |     |

| 10.1 Register-Controlled Power Management                               |     |

| 10.2 Instruction-Controlled Power Management                            |     |

| Ŭ                                                                       |     |

| Chapter 11 EJTAG Debug Support                                          |     |

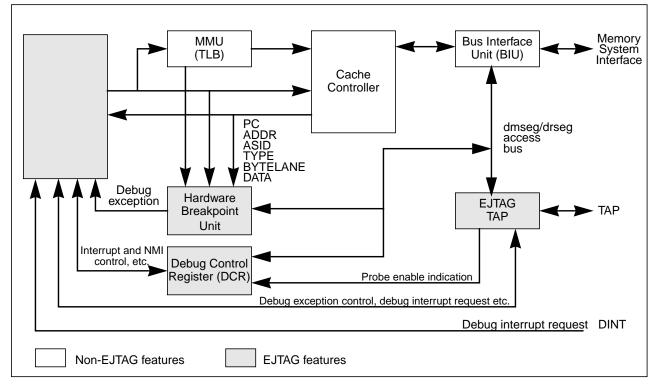

| 11.1 EJTAG Components and Options                                       |     |

| 11.1.1 EJTAG Extensions to the MIPS Processor Core                      |     |

| 11.1.2 Debug Control Register                                           |     |

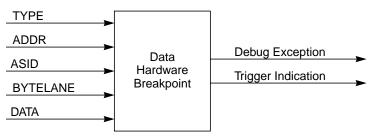

| 11.1.3 Hardware Breakpoint Unit                                         |     |

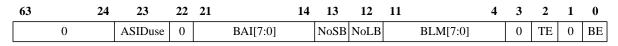

| 11.1.4 EJTAG Test Access Port                                           |     |

| 11.2 Register and Memory Map Overview                                   |     |

| 11.2.1 Coprocessor 0 Register Overview                                  |     |

| 11.2.2 Memory-Mapped EJTAG Register Overview                            |     |

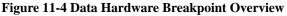

| 11.2.3 Data Hardware Breakpoint Register Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.2.4 Register Field Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                        |

| 11.3 EJTAG Processor Core Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        |

| 11.3.1 Debug Mode Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |

| 11.3.2 Debug Mode Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |

| 11.3.3 Debug Mode Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                        |

| 11.3.4 Debug Mode Handling of Processor Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |

| 11.3.5 Debug Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                        |

| 11.3.6 Debug Mode Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                        |

| 11.3.7 Interrupts and NMIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                        |

| 11.3.8 Reset and Soft Reset of the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                        |

| 11.3.9 EJTAG Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                        |

| 11.3.10 EJTAG Coprocessor 0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

| 11.4 Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |

| 11.5 Hardware Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                        |

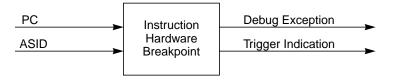

| 11.5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |

| 11.5.2 Overview of Instruction and Data Breakpoint Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                        |

| 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |

| 11.5.3 Conditions for Matching Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                        |

| 11.5.4 Debug Exceptions from Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                        |

| 11.5.5 Breakpoints Used as Triggerpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                        |

| 11.5.6 Instruction Breakpoint Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                        |

| 11.5.7 Data Breakpoint Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        |

| 11.6 EJTAG Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |

| 11.6.1 TAP Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                        |

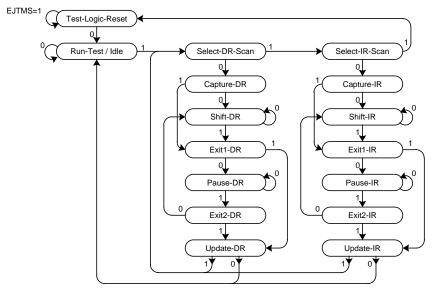

| 11.6.2 TAP Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

| 11.6.3 Test-Logic-Reset State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                        |

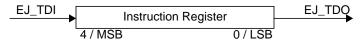

| 11.6.4 Instruction Register and Special Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        |

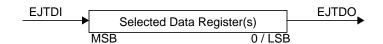

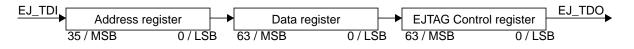

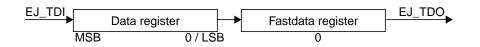

| 11.6.5 Data Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                        |

| Chapter 12 20Kc Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                        |

| Chapter 12 20Kc Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode<br>12.1.1 Cache Test Mode Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                        |

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 231<br>231<br>231<br>232<br>232<br>234<br>234<br>234<br>235<br>235                                                                                                                                                     |

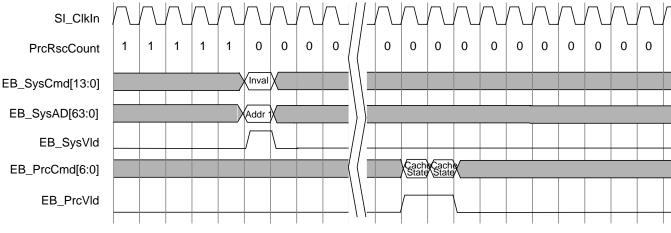

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings         12.1.8 Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 231<br>231<br>231<br>232<br>232<br>234<br>234<br>234<br>235<br>235<br>239                                                                                                                                              |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings         12.1.8 Protocols         12.2 PLL Bypass Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 231<br>231<br>231<br>232<br>232<br>234<br>234<br>235<br>235<br>235<br>239<br>240                                                                                                                                       |

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> <li>12.1.7 Encodings</li> <li>12.1.8 Protocols</li> <li>12.2 PLL Bypass Mode</li> <li>12.3 BIST (Built-In Self Test)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         | 231<br>231<br>231<br>232<br>234<br>234<br>234<br>235<br>235<br>235<br>239<br>240<br>241                                                                                                                                |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings         12.1.8 Protocols         12.2 PLL Bypass Mode         12.3 BIST (Built-In Self Test)         12.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                               | 231<br>231<br>231<br>232<br>234<br>234<br>234<br>235<br>235<br>235<br>239<br>240<br>241<br>241                                                                                                                         |

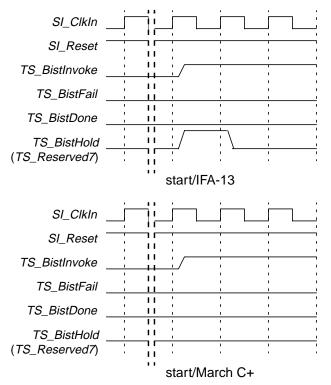

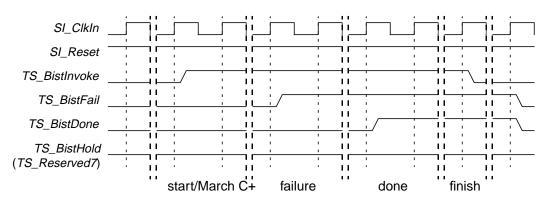

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> <li>12.1.7 Encodings</li> <li>12.1.8 Protocols</li> <li>12.2 PLL Bypass Mode</li> <li>12.3 BIST (Built-In Self Test)</li> <li>12.3.1 Overview</li> <li>12.3.2 Algorithms for Memory Test</li> </ul>                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |

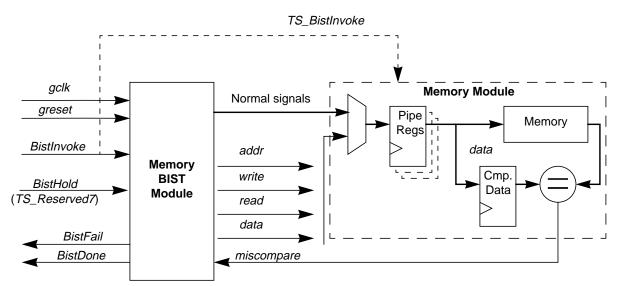

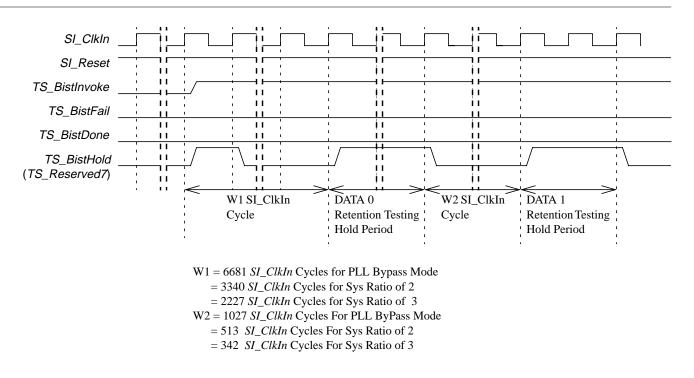

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> <li>12.1.7 Encodings</li> <li>12.1.8 Protocols</li> <li>12.2 PLL Bypass Mode</li> <li>12.3 BIST (Built-In Self Test)</li> <li>12.3.1 Overview</li> <li>12.3.2 Algorithms for Memory Test</li> <li>12.3.3 BIST Integration on 20Kc Cache Memories</li> </ul>                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> <li>12.1.7 Encodings</li> <li>12.1.8 Protocols</li> <li>12.2 PLL Bypass Mode</li> <li>12.3 BIST (Built-In Self Test)</li> <li>12.3.1 Overview</li> <li>12.3.2 Algorithms for Memory Test</li> </ul>                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |

| <ul> <li>12.1 Cache Test Mode</li> <li>12.1.1 Cache Test Mode Interface Signals</li> <li>12.1.2 System Interface Clock Divisor and Mode</li> <li>12.1.3 Entering Cache Test Mode</li> <li>12.1.4 Exit from Cache Test Mode</li> <li>12.1.5 Cache Test Mode Commands</li> <li>12.1.6 Read/Write Granularity</li> <li>12.1.7 Encodings</li> <li>12.1.8 Protocols</li> <li>12.2 PLL Bypass Mode</li> <li>12.3 BIST (Built-In Self Test)</li> <li>12.3.1 Overview</li> <li>12.3.2 Algorithms for Memory Test</li> <li>12.3.3 BIST Integration on 20Kc Cache Memories</li> <li>12.3.4 Cycles for Memory BIST Testing</li> </ul>                                                                                                                                                                                                                              | 231<br>231<br>231<br>232<br>234<br>234<br>234<br>235<br>235<br>235<br>239<br>240<br>240<br>241<br>241<br>241<br>244<br>244<br>245<br>246                                                                               |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings         12.1.8 Protocols         12.2 PLL Bypass Mode         12.3.1 Overview         12.3.2 Algorithms for Memory Test         12.3.3 BIST Integration on 20Kc Cache Memories         12.3.4 Cycles for Memory BIST Testing                                                                                                                                                                                                                                                                                                       | 231<br>231<br>231<br>232<br>234<br>234<br>235<br>235<br>235<br>239<br>240<br>240<br>241<br>241<br>241<br>241<br>244<br>245<br>246<br>247                                                                               |

| 12.1 Cache Test Mode         12.1.1 Cache Test Mode Interface Signals         12.1.2 System Interface Clock Divisor and Mode         12.1.3 Entering Cache Test Mode         12.1.4 Exit from Cache Test Mode         12.1.5 Cache Test Mode Commands         12.1.6 Read/Write Granularity         12.1.7 Encodings         12.1.8 Protocols         12.2 PLL Bypass Mode         12.3.1 Overview         12.3.2 Algorithms for Memory Test         12.3.3 BIST Integration on 20Kc Cache Memories         12.3.4 Cycles for Memory BIST Testing         Chapter 13 Instruction Set Architecture         13.1 CPU Architecture                                                                                                                                                                                                                         | 231<br>231<br>231<br>232<br>234<br>234<br>235<br>235<br>235<br>239<br>240<br>240<br>241<br>241<br>241<br>244<br>244<br>245<br>246<br>247                                                                               |